时间: 2024-02-24 09:57:14 | 作者: Z系列

以下是算整形平方根的IP核,如果计算浮点数,可以用浮点数的平方根IP核。

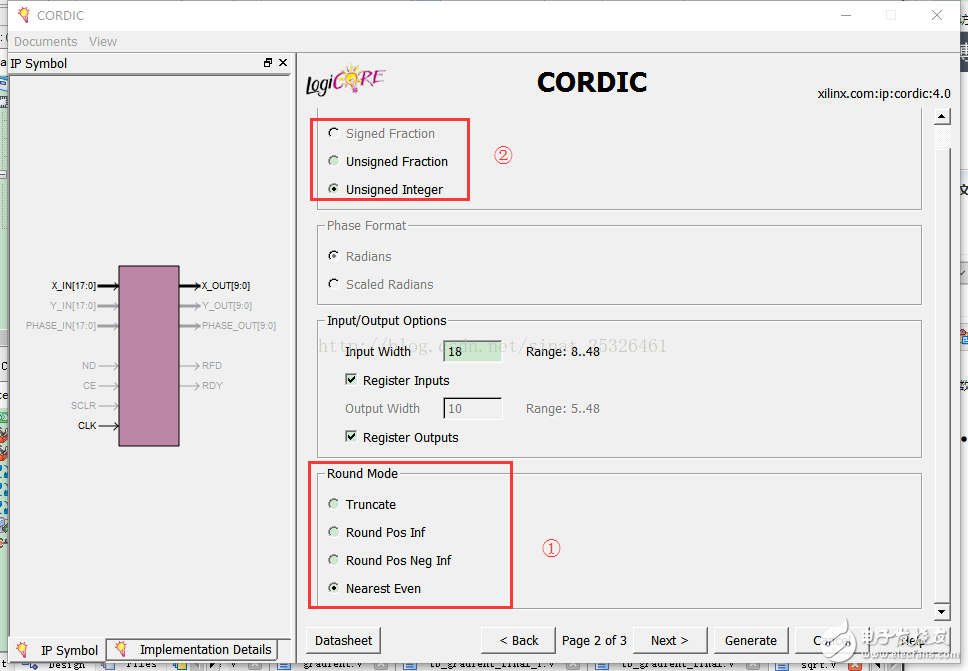

第二种:Round Pos Inf:四舍五入,+0.5之后四舍五入,在负数时和第三种有区别。

首先是“管理”-》“全局设定”-》“常规”-》默认虚拟电脑位置:选择一个专门用来放置虚拟机的位置,并...

在线路内对冲场景下,来自以太网接口的流量将被传递至FPGA以实现网络分流,而后被交付至Connect...

频谱分析仪是一种测试测量设备,大多数都用在射频和微波信号的频域分析,包括测量信号的功率,频率,失真等。它...

PrecisionFDA平台是基因组信息学社区和共享数据平台,这是一个为研究人员准备的开源、基于云的...

为了简化编码解码器和PL之间的集成复杂度,这里介绍两个AVNET所开发的IP核,可通过Avnet G...

随着人工智能(AI)的持续不断的发展,它已经从早期的人工特征工程进化到现在可以从海量数据中学习,机器视觉、...

xilinx官方实例代码如下,其实大概意思就是一个高电平之后,变成低电平。然后再高电平,等待tlas...

对于IP核输出数据的解析最好的工具就是其自带的仿真文件,里面既将接收的数据来进行了解析,又将发送给IP...

这个参数确定的是移位寄存器的移位时钟个数。这个时钟个数取决于后面的Depth参数。其中第一个参数Fi...

在生成滤波器IP核之前需要产生抽头系数,这个抽头系数的阶数是自己设定的,阶数越高代表滤波器乘累加运算...

JESD204B协议是目前高速AD,DA通用的协议。对于基带使用FPGA用户来说,Xilinx品牌的...

Xilinx以制造 可编程门阵列(FPGA)而闻名,它是基于一个通过可编程接点连接的可配置逻辑块(C...

随着信息技术的发展,特别是各种数字处理器处理速度的提高,人们对数据采集系统的要求慢慢的升高,特别是在一...

该委员会专门设计用于与来自锡林克斯的PYNQ项目合作,并使用Python语言和库,设计师可以创建高性...

数字电路设计中一般来说包括3个大的阶段:源代码输入、综合和实现,而电路仿真的切入点也基本与这些阶段相吻合...

近年来,ASIC设计规模的增大带来了前所未有的芯片原型验证问题,单颗大容量的FPGA通常已不足以容下...

Spartan-6系列具有低成本、省空间的封装形式,能使用户引脚密度最大化。所有Spartan-6...

网卡在功能上包含OSI模型的两个层,数据链路层和物理层。物理层定义了数据传送与接收所需要的电与光信号...

自适应和智能计算的全球领先企业赛灵思公司(Xilinx, Inc.,(NASDAQ:XLNX))和戴...

UFDM建议正确的HDL coding风格来满足目标器件,讨论时序约束和时序收敛。正确的IO约束,I...

Xilinx 7系列FPGA的HP bank都支持DCI,目的是在高速单板信号传输中保持信号完整性,...

项目设计初期会选型,工程师根据资源、IO、硬核、IP等选择对应型号的FPGA。功耗部分xilinx提...

开发机器视觉系统常常要大量的时间来设计能执行所有重要图像采集及处理功能的电子科技类产品。常常要两年多的...

在开放式协作服务爆炸性增长以及移动和社交网络持续不断的发展的推动下,结合智能设备的普及以及不同服务供应商与...

Xilinx FPGA 可提供卓越的数字信号处理 (DSP) 性能,能够很好的满足音频处理、接口、压缩、嵌...

通过消除繁琐的驾驶动作,辅助驾驶还可提供更高的舒适水平。例如,传统的巡航控制允许司机设定一个固定的行...

如果升级过程中发生意外情况,FLASH里面原有的固件被破坏,那么FPGA能够从备份固件区启动配置,即...

你有没有注意到在Netflix流媒体视频播放时,有时候视频模糊,然后很快恢复到高质量? 你知道Net...

你有没有注意到在Netflix流媒体视频播放时,有时候视频模糊,然后很快恢复到高质量? 你知道Net...

本视频教程主要主要介绍Xilinx公司开发设计流程中的各个功能模块,包括ISE中的设计输入,综合,设...

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

GigE Vision是一个基于以太网技术的标准化视频应用的通信协议。可以轻轻松松实现GigE Visi...

10多年来,慢慢的变多的应用已采用嵌入式计算机架构,将基于ARM的不同SoC和FPGA整合在同一印刷电...

整个行业都在力求降低功耗和材料清单成本,同时增大典型面板上的可用光通量,这可利用尺寸更小速度更快...

除了要最终客户推出屡获殊荣的Zynq-7000 AP SoC器件帮他们在竞争中整整领先一代之外,我...

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

Xilinx公司面向大批量应用的的Artix-7 FPGA的能耗优势演示。

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

Virtex-7 FPGA系列旨在满足宽带通信、高阶无线基础设施、高端数字广播、雷达图像处理及其它航...

在理解了SDSoC“平台”的概念之后(详见《SDSoC上手必读:什么是SDSoC平台?》),现在我们...

AD9739A FMC板基于14位DAC,能够让有线电视和宽带运营商将高至1 GHz的整个电缆频谱合...

此视频由Sensor to Image公司为您展示了不同高速协议下的机器视觉摄像头和帧图像采集卡中的...

Martin Gilpatric教您处理在调试收发器设计时常见的一个串行链接问题,

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

本文介绍一下xilinx的开发软件 vivado 的仿真模式, vivado的仿真暂分为五种仿真模式...

大家好,又到了每日学习的时间了,最近有很多人再问我学习FPGA到底是选择Altera的还是xilin...

在xilinx下每种操作其实都对应着一种工具,逻辑综合,网表与constraint fie的合并,布...

大家好,今天咱们聊聊 xilinx FPGA bit 文件加密 ,当你的项目终于做完了,到了发布的关...

在,大家都认为串行链路的构建难度大,尤其是对10Gb以上的系统,您一定要解决系统中的插入损耗,反射串扰...

移动IP的使用呈爆炸式增长态势,据国际电信联盟(ITU),信息与通信技术(ICT)报告称,在2000...

真正的开源技术,基于Zynq-7000的软件与硬件灵活性,适用于工业控制和工业实时以太网的POWER...

采用Z7020实现的高性能马达控制可以又小地减少振动和电磁干扰。Zynq-7000软件/硬件架构可以...

此次为期30分钟的视频演示介绍了 Xilinx 提供的 DSP 设计工具。我们从带有浮点 MATLA...

设计人员呼吁提升10G+ 芯片到芯片和背板性能, 依赖接收机均衡来补偿信号失真。观看视频, 并排比较...

这个培训将会深度介绍适于Xililnx 可编程门阵列的HDL代码风格, 产生和验证时序约束的正确方法...

Xilinx 宣布启动一项将软件、模型、平台和基于 IP 的设计环境融为一体的抽象化计划,致力于让系...

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能...

上一篇:2023 第七届集成电路创新创业大赛启动“飞腾杯” 赛道如约而来关于我们

爱游戏体育app合作罗马

Z系列 M系列 W系列成功案例

五金配件 爱游戏体育app合作伙伴罗马新闻中心

爱游戏体育app合作伙伴罗马_爱游戏ayx全站 行业新闻联系我们

网站地图